| OTTO VON GUERICKE<br>UNIVERSITÄT<br>MAGDEBURG | MATH | FAKULTÄT FÜF<br>MATHEMATIK |

|-----------------------------------------------|------|----------------------------|

|                                               |      |                            |

## Lecture Notes

## "Scientific Computing II"

Summer Term 2021

Dr.Jens Saak

jens.saak

@mpi-magdeburg.mpg.de

Dipl.-Math. Martin Köhler martin.koehler @mpi-magdeburg.mpg.de

| II |  |  |

|----|--|--|

|  | <br> |         |

|--|------|---------|

|  |      | Preface |

|  |      |         |

iν

## Contents

|   | Pre  | ace                                              | iii |

|---|------|--------------------------------------------------|-----|

| 1 | Intr | duction                                          | 1   |

|   | 1.1  | Why Parallel Computing?                          | 1   |

|   | 1.2  | Flynn's Taxonomy of Parallel Architectures       | 2   |

|   |      | 1.2.1 Single-Instruction, Single-Data (SISD)     | 3   |

|   |      | 1.2.2 Multiple-Instruction, Single-Data (MISD)   | 4   |

|   |      | 1.2.3 Single-Instruction, Multiple-Data (SIMD)   | 4   |

|   |      | 1.2.4 Multiple-Instruction, Multiple-Data (MIMD) | 5   |

|   | 1.3  | Memory Hierarchies in Parallel Computers         | 7   |

|   |      | 1.3.1 Repetition Sequential Processor            | 7   |

|   |      | 1.3.2 Shared Memory                              | 8   |

|   |      | 1.3.3 General Memory Setting                     | 10  |

|   | 1.4  | Communication Networks                           | 10  |

|   |      | 1.4.1 Hardware                                   | 10  |

|   |      | 1.4.2 Topologies                                 | 11  |

| 2 | Per  | ormance Measures                                 | 13  |

|   | 2.1  | Time Measurement and Operation Counts            | 13  |

|   |      | 2.1.1 The Single Processor Case                  | 13  |

|   |      | 2.1.2 Instructions: Timings and Counts           | 14  |

|   |      | 2.1.3 MIPS versus FLOPS                          | 15  |

|   |      |                                                  | 15  |

|   | 2.2  | Parallel Cost                                    | 16  |

|   | 2.3  |                                                  | 17  |

|   | 2/   | Parallel Efficiency                              | 17  |

i Contents

|   | 2.5 | Amda   | <mark>hl's Law</mark>                                           |

|---|-----|--------|-----------------------------------------------------------------|

|   | 2.6 | Scalab | oility of Parallel Programs                                     |

|   |     |        |                                                                 |

| 3 |     |        | and Multiprocessor Systems 21                                   |

|   | 3.1 | Symm   | netric Multiprocessing                                          |

|   | 3.2 |        | ory Hierarchy                                                   |

|   |     | 3.2.1  | Basic Memory Layout                                             |

|   |     | 3.2.2  | UMA                                                             |

|   |     | 3.2.3  | NUMA                                                            |

|   |     | 3.2.4  |                                                                 |

|   | 3.3 |        | sses and Threads                                                |

|   |     | 3.3.1  | Multiprocessing                                                 |

|   |     | 3.3.2  | Threading                                                       |

|   |     | 3.3.3  | Mapping of user level threads to kernel threads or processes 26 |

|   |     | 3.3.4  | Properties and Problems                                         |

|   |     | 3.3.5  | Protection of critical regions                                  |

|   |     | 3.3.6  | Dining Philosophers                                             |

|   | 3.4 |        | Threads                                                         |

|   |     | 3.4.1  | Basics                                                          |

|   |     | 3.4.2  | Creation of threads                                             |

|   |     | 3.4.3  | Exiting threads and waiting for their termination 31            |

|   | 3.5 |        | ad coordination mechanisms                                      |

|   |     | 3.5.1  | Mutex and condition variables                                   |

|   |     | 3.5.2  | Mutex variables                                                 |

|   |     | 3.5.3  | Avoiding mutex triggered deadlocks                              |

|   |     | 3.5.4  | Condition variables                                             |

|   |     | 3.5.5  | A counting semaphore for Pthreads                               |

|   |     | 3.5.6  | A typical application example for semaphores 37                 |

|   |     | 3.5.7  | Coordination models for the cooperation of threads 38           |

|   | 3.6 |        | Pools                                                           |

|   |     | 3.6.1  | Basic idea of the task pool                                     |

|   |     | 3.6.2  | Implementation of a basic task pool                             |

|   | 3.7 |        | d Memory Blocks                                                 |

|   |     | 3.7.1  | General shared memory blocks                                    |

|   |     | 3.7.2  | POSIX Shared Memory                                             |

|   | 3.8 |        | MP                                                              |

|   |     | 3.8.1  | This is OpenMP                                                  |

|   |     | 3.8.2  | What OpenMP can do for us                                       |

|   |     | 3.8.3  | What OpenMP is NOT for!                                         |

|   |     | 3.8.4  | The Structure of the Standard                                   |

|   |     | 3.8.5  | OpenMP directives                                               |

|   |     | 3.8.6  | OpenMP clauses                                                  |

|   |     | 3.8.7  | OpenMP Environment Variables                                    |

|   |     | 3.8.8  | OpenMP runtime library functions                                |

| Contents | vi |

|----------|----|

|----------|----|

|   | 3.9   | Tree Reduction                                                    | 59  |

|---|-------|-------------------------------------------------------------------|-----|

|   |       | 3.9.1 The OpenMP reduction minimal example revisited              | 59  |

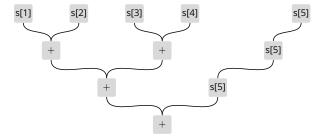

|   |       | 3.9.2 Basic idea of tree reduction                                | 59  |

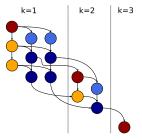

|   |       | 3.9.3 Practical tree reduction on multiple cores                  | 60  |

|   | 3.10  | Dense Linear Systems                                              | 60  |

|   |       |                                                                   | 60  |

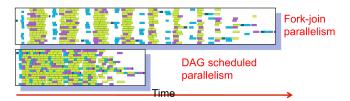

|   |       | 3.10.2 Fork-Join parallel implementation for multicore machines . | 62  |

|   |       | 3.10.3 DAG scheduling of block operations aiming at manycore      |     |

|   |       | systems                                                           | 63  |

|   | 3.11  | Sparse Linear Systems                                             | 64  |

|   |       | 3.11.1 The Conjugate Gradient (CG) Method (a prototype iterative  |     |

|   |       | solver)                                                           | 64  |

|   |       | 3.11.2 Sparse Matrix Vector Products                              | 65  |

|   |       | 3.11.3 Preconditioning                                            | 67  |

|   |       |                                                                   | 68  |

|   |       | 3.11.5 Diagonal/Jacobi Preconditioner                             | 68  |

|   |       | 3.11.6 Sparse Approximate Inverse (SPAI) Preconditioning          | 68  |

|   |       |                                                                   | 69  |

|   |       |                                                                   | 72  |

|   | 3.12  | Software                                                          | 73  |

|   | 51.12 |                                                                   |     |

| 4 |       | Computing and Accelerators                                        | 75  |

|   |       | Why use accelerators?                                             | 76  |

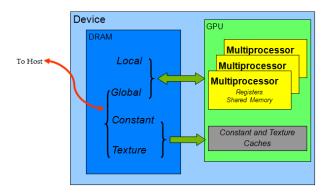

|   | 4.2   |                                                                   | 77  |

|   |       | 4.2.1 Common Features                                             | 77  |

|   |       | 4.2.2 GPUs                                                        | 78  |

|   |       | 4.2.3 FPGAs                                                       | 78  |

|   | 4.3   | CUDA                                                              | 78  |

|   |       | 4.3.1 What is CUDA?                                               | 78  |

|   |       |                                                                   | 79  |

|   |       | 4.3.3 Most Basic Syntax of the CUDA C Extension                   | 81  |

|   |       |                                                                   | 82  |

|   |       | 4.3.5 Compiling CUDA Programs                                     | 84  |

|   |       | 4.3.6 Compute Capabilities                                        | 85  |

|   |       | 8                                                                 | 86  |

|   |       |                                                                   | 87  |

|   |       | 4.3.9 The CUDA Application Programmers Interface                  | 91  |

|   |       |                                                                   | 94  |

|   |       | ,                                                                 | 94  |

|   |       | · · · · · · · · · · · · · · · · · · ·                             | 95  |

|   |       |                                                                   | 96  |

|   |       | <b>4.3.14 Other Topics</b>                                        | 103 |

|   | 4.4   |                                                                   | 103 |

|   | 4.5   | Linear Systems                                                    | 104 |

|   |       |                                                                   |     |

viii Contents

|   | 4.6  | 4.5.1<br>4.5.2<br>4.5.3<br>Software<br>4.6.1<br>4.6.2 | The block outer product LU decomposition revisited Iterative Linear System Solvers Sparse Iterative Eigenvalue Approximation are | 104<br>105<br>105<br>105<br>105<br>106 |

|---|------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 5 | Dist | ribute                                                | d Memory Systems                                                                                                                 | 111                                    |

|   | 5.1  | Memo                                                  | ory Hierarchy                                                                                                                    | 112                                    |

|   | 5.2  | Comp                                                  | arison of Distributed Memory Systems                                                                                             | 112                                    |

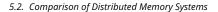

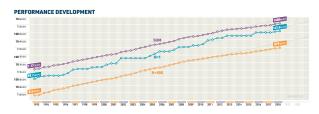

|   |      | 5.2.1                                                 | Rankings                                                                                                                         | 112                                    |

|   |      | 5.2.2                                                 | Architectural Streams Currently Pursued                                                                                          | 113                                    |

|   |      | 5.2.3                                                 |                                                                                                                                  | 114                                    |

|   |      | 5.2.4                                                 | Manycore and Embedded Hosts                                                                                                      | 114                                    |

|   |      | 5.2.5                                                 | Multicore CPU Hosts                                                                                                              | 114                                    |

|   |      | 5.2.6                                                 | The 2020 vision: Exascale Computing                                                                                              | 115                                    |

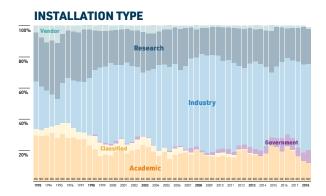

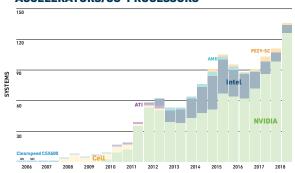

|   |      | 5.2.7                                                 | State of the art (statistics)                                                                                                    | 116                                    |

|   | 5.3  |                                                       | nunication                                                                                                                       | 118                                    |

|   |      | 5.3.1                                                 | Communication via Message Passing                                                                                                | 118                                    |

|   | 5.4  |                                                       | nunication Networks (revisited)                                                                                                  | 121                                    |

|   |      | 5.4.1                                                 | Asymptotic Message runtimes in some Standard Network                                                                             |                                        |

|   |      |                                                       | Topologies                                                                                                                       | 121                                    |

|   |      | 5.4.2                                                 | Some Remarks on the Hypercube                                                                                                    | 126                                    |

|   |      | 5.4.3                                                 |                                                                                                                                  | 127                                    |

|   | 5.5  | 5.5.1                                                 | age Passing Interface API                                                                                                        | 131<br>131                             |

|   |      | 5.5.1                                                 | Process Groups and Communicators                                                                                                 | 132                                    |

|   |      | 5.5.3                                                 | Point-to-Point Communication                                                                                                     | 135                                    |

|   |      | 5.5.4                                                 | Single-Collective Communication                                                                                                  | 136                                    |

|   |      | 5.5.5                                                 | Multi-Collective Communication                                                                                                   | 138                                    |

|   | 5.6  |                                                       | age Passing using Open MPI                                                                                                       | 139                                    |

|   | 5.7  | Data I                                                | Distribution Schemes in Distributed LU                                                                                           | 141                                    |

|   | 5.7  | 5.7.1                                                 |                                                                                                                                  | 142                                    |

|   |      | 5.7.2                                                 |                                                                                                                                  | 143                                    |

|   |      | 5.7.3                                                 |                                                                                                                                  | 144                                    |

|   |      | 5.7.4                                                 |                                                                                                                                  |                                        |

|   |      |                                                       | PACK                                                                                                                             | 145                                    |

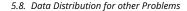

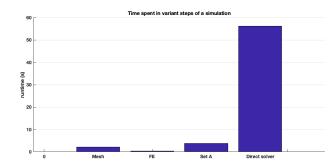

|   | 5.8  |                                                       | Distribution for other Problems                                                                                                  |                                        |

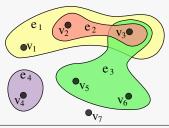

|   |      | 5.8.1                                                 | Algebraic Domain Decomposition                                                                                                   | 147                                    |

|   | 5.9  | Softw                                                 | are                                                                                                                              | 150                                    |

## CHAPTER 1

|  | ١Ť |  |  |  |  |  |

|--|----|--|--|--|--|--|

|  |    |  |  |  |  |  |

|  |    |  |  |  |  |  |

| Contents |                                                    |  |

|----------|----------------------------------------------------|--|

| 1.1      | Why Parallel Computing?                            |  |

| 1.2      | Flynn's Taxonomy of Parallel Architectures         |  |

|          | 1.2.1 Single-Instruction, Single-Data (SISD) 3     |  |

|          | 1.2.2 Multiple-Instruction, Single-Data (MISD) 4   |  |

|          | 1.2.3 Single-Instruction, Multiple-Data (SIMD) 4   |  |

|          | 1.2.4 Multiple-Instruction, Multiple-Data (MIMD) 5 |  |

| 1.3      | Memory Hierarchies in Parallel Computers           |  |

|          | 1.3.1 Repetition Sequential Processor              |  |

|          | 1.3.2 Shared Memory                                |  |

|          | 1.3.3 General Memory Setting                       |  |

| 1.4      | Communication Networks                             |  |

|          | 1.4.1 Hardware                                     |  |

|          | 1.4.2 Topologies                                   |  |

## 1.1 Why Parallel Computing?

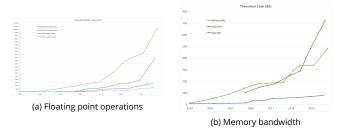

Classically the area of Scientific Computing, or more precisely that of High Performance Computing (HPC) has been the major source for the demand on parallel computing techniques and abilities. Nowadays the picture is changing drastically due to the emerging field of multi and many Core architectures. In only

a few years of time one has to expect computer programs of all kinds to have to run on highly parallel desktop computers. Therefore, we can currently state three important reasons for the interest in parallel computing techniques:

- 1. Problem size exceeds desktop capabilities.

- 2. Problem is inherently parallel (e.g. Monte-Carlo simulations).

- Modern architectures require parallel programming skills to take best adavatage of their features.

Here, the last one is clearly the modern one that has come up with the availability of MultiCore processors in basically all modern devices starting from desktop computers, possibly equipped with high performance graphics processing units (GPUs), but also reaching down to modern smart-phones with MultiCore mobile processors. The first two are more classical approaches requiring specialized HPC hardware or networks of many standard PCs (the so called *Clusters*). Although especially for the second MultiCore processors may give a huge impact, too.

## 1.2 Flynn's Taxonomy of Parallel Architectures

The basic definition of a parallel computer is very vague in order to cover a large class of systems. Important details that are not considered by the definition are:

- How many processing elements?

- · How complex are they?

- · How are they connected?

- How is their cooperation coordinated?

- What kind of problems can be solved?

The basic classification allowing answers to most of these questions is known as *Flynn's taxonomy*. It distinguishes four categories of parallel computers.

The four categories allowing basic answers to the questions on global process control, as well as the resulting data and control flow in the machine are

- 1. Single-Instruction, Single-Data (SISD)

- 2. Multiple-Instruction, Single-Data (MISD)

- 3. Single-Instruction, Multiple-Data (SIMD)

- 4. Multiple-Instruction, Multiple-Data (MIMD)

All four of these serve as *machine models* for different kinds of actual hardware implementations. The models with their properties subdivisions and example hardware are discussed in the next few sections.

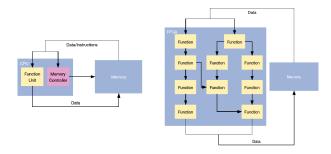

#### 1.2.1 Single-Instruction, Single-Data (SISD)

The most simple and classically most common architectural model is the single-instruction, single-data model. It represents what has been the standard for desktop computers until the introduction of MultiCore processors only a few years ago. The SISD model is characterized by

- · a single processing element,

- · executing a single instruction,

- · on a single piece of data,

- · in each step of the execution.

It is thus in fact the standard sequential computer implementing, e.g., the  $\emph{von Neumann}$  model<sup>1</sup>.

#### Examples

- · desktop computers until Intel® Pentium® 4 era,

- early netBooks on Intel<sup>®</sup> Atom™ basis,

- · pocket calculators,

- · abacus.

- · embedded circuits

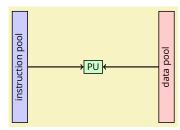

A schematic presentation of the model is given in Figure 1.1.

Figure 1.1: Single-Instruction, Single-Data (SISD) machine model

<sup>1</sup>see, e.g., http://en.wikipedia.org/wiki/Von\_Neumann\_architecture

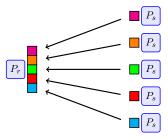

#### 1.2.2 Multiple-Instruction, Single-Data (MISD)

In contrast to the SISD model in the MISD architecture we have

- · multiple processing elements,

- · executing a separate instruction each,

- · all on the same single piece of data,

- in each step of the execution.

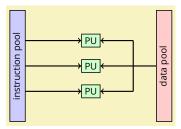

The MISD model is usually not considered very useful in practice. Figure 1.2 shows the graphical representation of this model.

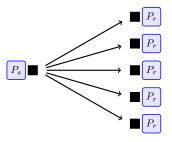

Figure 1.2: Multiple-Instruction, Single-Data (MISD) machine model

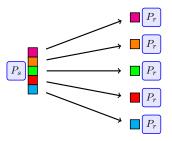

#### 1.2.3 Single-Instruction, Multiple-Data (SIMD)

The single-instruction, multiple-data model is a much more useful approach compared to MISD. Here the characterization is

- · multiple processing elements,

- · execute the same instruction,

- · on a multiple pieces of data,

- in each step of the execution.

This model is thus the ideal model for all kinds of vector operations

$$c = a + \alpha b$$

.

Here for every triple of entries in a,b, and c we have to perform the same three instructions. First we scale the entry in b, then add it to the corresponding entry in a and store the result to the appropriate position in c.

#### **Examples**

- · Graphics Processing Units,

- · Vector Computers,

- SSE (Streaming SIMD Extension) registers of modern CPUs.

The attractiveness of the SIMD model for vector operations, i.e., linear algebra operations, comes at a cost.

Consider the simple conditional expression

```

if (b==0) c=a; else c=a/b;

```

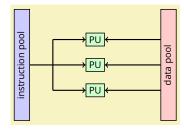

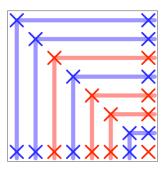

The SIMD model requires the execution of both cases sequentially. First all processes for which the condition is true execute their assignment, then the other do the second assignment. Therefore, conditionals need to be avoided on SIMD architectures to guarantee maximum performance. Figure 1.3 makes it even more obvious that SIMD architectures are ideal to utilize *data level parallelism*.

The SIMD model is characterized by the "run the same set of operations at the same time in parallel" paradigm. This is helpful in vector operations as seen above, but brings in the restrictions for conditionals we have also seen. The SPMD model described in the next section as one subclass of the MIMD model weakens this restriction.

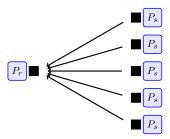

Figure 1.3: Single-Instruction, Multiple-Data (SIMD) machine model

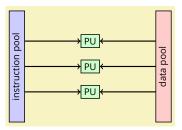

#### 1.2.4 Multiple-Instruction, Multiple-Data (MIMD)

The most flexible architectural approach is described by the multiple-instruction, multiple-data model.  $\,$  MIMD allows  $\,$

- · multiple processing elements,

- · to execute a different instruction.

- · on a separate piece of data,

- · at each instance of time.

#### **Examples**

- · multicore and multi-processor desktop PCs,

- · cluster systems.

MIMD computer systems can be further divided into three class regarding their memory configuration:

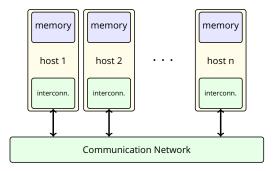

#### distributed memory

Every processing element has a certain exclusive portion of the entire memory available in the system. Data needs to be exchanged via an interconnection network. These machines will be treated in more detail in Chapter 5.

#### shared memory

All processing units in the system can access all data in the main memory. Several different models describing the uniformity of the access like UMA, NUMA, and ccNUMA will be treated in Chapter 3.

#### hybrid

Certain groups of processing elements share a part of the entire data and instruction storage.

When working with MIMD systems users basically follow either of the following two programming models.

#### Single Program, Multiple Data (SPMD)

SPMD is a programming model for MIMD systems. "In SPMD multiple autonomous processors simultaneously execute the same program at independent points." This contrasts to the SIMD model where the execution points are not independent.

This is opposed to

#### Multiple Program, Multiple Data (MPMD)

A different programming model for MIMD systems, where multiple autonomous processing units execute different programs at the same time. Typically Master/Worker like management methods of parallel programs are associated with this class. There the Master is acting as a controller process executing a different programs than its Workers performing the actual computations.

<sup>2</sup>Wikipedia: http://en.wikipedia.org/wiki/SPMD

Figure 1.4: Multiple-Instruction, Multiple-Data (MIMD) machine model

#### 1.3 Memory Hierarchies in Parallel Computers

#### 1.3.1 Repetition Sequential Processor

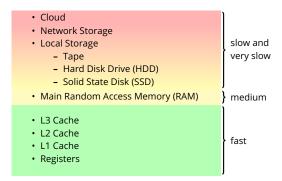

Recall the basic ideas for the memory hierarchy on a sequential system we have discussed in Chapter 4 of the first part of this lecture. We have classified several types of storage into fast medium speed and slow storage/memory. Based on this classification we derived strategies for data management to optimize the run-time of a program executing a certain variant of an algorithm. For linear algebra operations this mainly lead to the reformulation of the algorithms in block matrix fashion where we could execute cubically many operations on quadratically many entries in terms of the matrix dimension. This turned out to be the optimal way of using the Caches on the processor.

Figure 1.5: Basic memory hierarchy on a single processor system.

## 1.3.2 Shared Memory

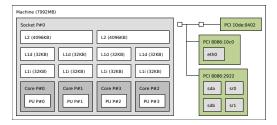

Figure 1.6: A sample dual core Xeon® setup

Figure 1.7: A sample Core™ 2 Quad setup

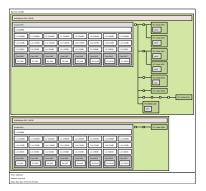

Figure 1.8: A four processor octa-core Xeon® system

Figure 1.9: A dual processor octa-core Xeon® system

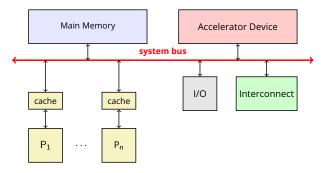

#### 1.3.3 General Memory Setting

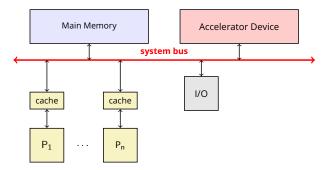

Figure 1.10: Schematic of a general parallel system

#### 1.4 Communication Networks

The **Interconnect** in the last figure stands for any kind of Communication grid. This can be implemented either as

· local hardware interconnect,

or in the form of

· network interconnect.

In classical supercomputers the first was mainly used, whereas in today's cluster based systems often the network solution is used in the one form or the other.

#### 1.4.1 Hardware

Network hardware is nowadays mainly one of the two types

#### MyriNet

- shipping since 2005

- transfer rates up to 10Gbit/s

- lower overhead compared to Ethernet

- · less interference of the actual transfer and CPU

• thus higher throughput

• lost significance (2005 28.2% TOP500 down to 0.8% in 2011)

#### Infiniband

- transfer rates up to 300Gbit/s

- features remote direct memory access (RDMA) → reduced CPU overhead

- can also be used for TCP/IP communication

#### Omni-Path

- transfer rates up to 100Gbit/s

- introduced by Intel<sup>®</sup> in 2015/2016

- · rising significance

- Intel<sup>®</sup>'s approach to address cluster of > 10000 nodes

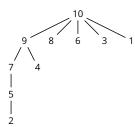

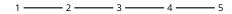

#### 1.4.2 Topologies

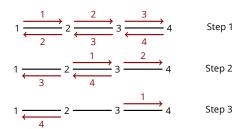

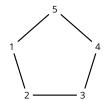

- Linear array: nodes aligned on a string each being connected to at most two neighbors.

- Ring: nodes are aligned in a ring each being connected to exactly two neighbors

- 3. **Complete graph:** every node is connected to all other nodes

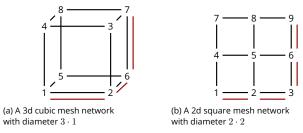

- 4. **Mesh and Torus:** Every node is connected to a number of neighbors (2–4 in 2d mesh, 4 in 2d torus).

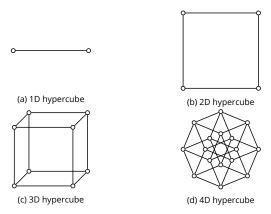

- 5. **k-dimensional cube / hypercube:** Recursive construction of a well connected network of  $2^k$  nodes each connected to k neighbors. Line for two, square for four, cube fore eight.

- 6. **Tree:** Nodes are arranged in groups, groups of groups and so forth until only one large group is left, which represents the root of the tree.

<sup>3</sup>http://www.openfabrics.org/

Chapter 1. Introduction

#### 12

## CHAPTER 2

## Performance Measures

## Contents

| 2 | .1 | Time Measurement and Operation Counts  |

|---|----|----------------------------------------|

|   |    | 2.1.1 The Single Processor Case        |

|   |    | 2.1.2 Instructions: Timings and Counts |

|   |    | 2.1.3 MIPS versus FLOPS                |

|   |    | 2.1.4 CPU_Time versus Execution Time   |

| 2 | .2 | Parallel Cost                          |

| 2 | .3 | Speedup                                |

| 2 | .4 | Parallel Efficiency                    |

| 2 | .5 | Amdahl's Law                           |

| 2 | .6 | Scalability of Parallel Programs       |

|   |    |                                        |

## 2.1 Time Measurement and Operation Counts

## 2.1.1 The Single Processor Case

## Definition 2.1:

In general we call the time elapsed between issuing a command and receiving its results the *runtime*, or *execution time* of the corresponding process. Some authors also call it elapsed time, or wall clock time.

In the purely sequential case it is closely related to the so called *CPU time* of the process. There the main contributions are:

- user CPU time: Time spent in execution of instructions of the process.

- system CPU time: Time spent in execution of operating system routines called by the process.

- waiting time: Time spent waiting for time slices, completion of I/O, memory fetches...

That means the time we have to wait for a response of the program includes the waiting times besides the CPU time. We have focused on minimizing the waiting times mainly caused by cache misses in part one of the lecture in winter term. Other waiting times caused by the overall load of the system are out of our reach anyway. Therefore, we will basically neglect this contribution for further considerations. The same holds for the system CPU time part. The time spent here strongly depends on the type and implementation of system calls in the underlying operating system, which we also can not influence. Only in multi-threading environments, where system calls (e.g. for storing intermediate results to disks) can be executed independent of the rest of the execution of the process, one should try and use threads (see Section 3.3.2) to minimize their influence.

In the following we have a closer look on the user CPU time contribution. A major part of this is due to the execution of different instructions issued by the program. The upcoming two sections will get into detail on the problems connected to varying instructions and the concepts of low and high level instructions.

#### 2.1.2 Instructions: Timings and Counts

#### clock rate and cycle time

The *clock rate* of a processor tells us how often it can switch instructions per second. Closely related is the *(clock) cycle time*, i.e., the time elapsed between two subsequent clock ticks.

#### Example 2.2:

A CPU with a clock rate of  $3.5~{\rm GHz}=3.5\cdot10^9$  1/s executes  $3.5\cdot10^9$  clock ticks per second. The length of a clock cycle thus is

$$1/(3.5 \cdot 10^9) \, \mathrm{s} = 1/3.5 \cdot 10^{-9} \cdot \mathrm{s} \approx 0.29 \, \mathrm{ns}$$

Different instructions require different times to get executed. This is represented by the so called *cycles per instruction* (CPI) of the corresponding instruc-

tion. An average CPI is connected to a process A via CPI(A).

This number determines the total user CPU time together with the number of instructions and cycle time via

$$T_{U\ CPU}(A) = n_{instr}(A) \cdot CPI(A) \cdot t_{cycle}$$

Clever choices of the instructions can influence the values of  $n_{instr}(A)$  and CPI(A).  $\leadsto$  compiler optimization.

#### 2.1.3 MIPS versus FLOPS

A common performance measure of CPU manufacturers is the *Million instructions per second (MIPS) rate*. It can be expressed as

$$MIPS(A) = \frac{n_{instr}(A)}{T_{U\ CPU}(A) \cdot 10^6} = \frac{r_{cycle}}{CPI(A) \cdot 10^6},$$

where  $r_{cucle}$  is the cycle rate of the CPU.

This measure can be misleading in high performance computing, since higher instruction throughput does not necessarily mean shorter execution time.

More common for the comparison in scientific computing is the rate of floating point operations (FLOPS) executed. The MFLOPS rate of a program  ${\cal A}$  can be expressed as

$$MFLOPS(A) = \frac{n_{FLOPS}(A)}{T_{UCPU}(A) \cdot 10^{6}} [1/s],$$

with  $n_{FLOPS}(A)$  the total number of FLOPS issued by the program A.

Note that not all FLOPS (see also Chapter 4 winter term) take the same time to execute. Usually divisions and square roots are much slower. The MFLOPS rate, however, does not take this into account.

#### 2.1.4 CPU\_Time versus Execution Time

On a parallel machine time measurement includes some notable side effects that are best explained by a simple example. The following is a simple script in MATLAB<sup>®</sup>.

Example 2.3 (A simple MATLAB test):

#### Input:

ct0=0;

**A=randn** (1500);

2.3. Speedup

tic

ct0=cputime;

pause(2)

toc

cputime-ct0

tic

ct0=cputime;

[0,R]=qr(A);

toc

cputime-ct0

#### Output:

The results have been obtained in MATLABR2010b on a system with four octacore Xeon $^{\$}$  processors.

Obviously, in a parallel environment the CPU time can be much higher than the actual execution time elapsed between start and end of the process.

In any case, it can be much smaller, as well.

The first result is easily explained by the splitting of the execution time into user/system CPU time and waiting time. The process is mainly waiting for the sleep system call to return whilst basically accumulating no active CPU time.

The second result is due to the fact that the activity is distributed to several cores. Each activity accumulates its own CPU time and these are summed up to the total CPU time of the process.

## 2.2 Parallel Cost and Optimality

**Definition 2.4** (Parallel cost and cost-optimality): The cost of a parallel program with data size n is defined as

$$C_p(n) = p * T_p(n).$$

Here  $T_p(n)$  is the  $\it parallel\ runtime$  of the process, i.e., its execution time on p processors.

The parallel program is called cost-optimal if

$$C_n = T^*(n).$$

Here,  $T^{st}(n)$  represents the execution time of the fastest sequential program solving the same problem.

In practice  $T^*(n)$  is often approximated by  $T_1(n)$ . This is due to the fact that the optimal algorithm for a problem is often not available for comparison, or not available at all. The later basically means that a proof of existence for the algorithm exists, but is not constructive so that the actual algorithm fulfilling the optimal sequential cost is unknown.

## 2.3 Speedup

The speedup of a parallel program

$$S_p(n) = \frac{T^*(n)}{T_p(n)},$$

is a measure for the acceleration, in terms of execution time, we can expect from a parallel program. The speedup is strictly limited from above by p since otherwise the parallel program would motivate a faster sequential algorithm. A method to derive such a sequential algorithm is described in [18, Chapter 4].

In practice often the speedup is computed with respect to the sequential version of the code, i.e.,

$$S_p(n) \approx \frac{T_1(n)}{T_p(n)}.$$

## 2.4 Parallel Efficiency

Usually, the parallel execution of the work a program has to perform comes at the cost of certain management of subtasks. Their distribution, organization

and interdependence leads to a fraction of the total execution, that has to be done extra.

#### Definition 2.5:

The fraction of work that has to be performed by a sequential algorithm as well is described by the *parallel efficiency* of a program. It is computed as

$$E_p(n) = \frac{T^*(n)}{C_p(n)} = \frac{S_p(n)}{p} = \frac{T^*}{p \cdot T_p(n)}.$$

The parallel efficiency obviously is limited from above by  $E_p(n)=1$  representing the perfect speedup of p. Since the values range from 0 to 1 the parallel efficiency is often also represented as a percent value, i.e.,  $E_p(n)$  is identified with  $100*E_p(n)$ .

#### 2.5 Amdahl's Law

In many situations it is impossible to parallelize the entire program. Certain fractions remain that need to be performed sequentially. When a (constant) fraction f of the program needs to be executed sequentially,  $Amdahl's\ law$  describes the maximum attainable speedup.

The total parallel runtime  $T_n(n)$  then consists of

- $f \cdot T^*(n)$  the time for the sequential fraction and

- $(1-f)/p \cdot T^*(n)$  the time for the fully parallel part.

The best attainable speedup can thus be expressed as

$$S_p(n) = \frac{T^*(n)}{f \cdot T^*(n) + \frac{1-f}{p}T^*(n)} = \frac{1}{f + \frac{1-f}{p}} \leqslant \frac{1}{f}.$$

## 2.6 Scalability of Parallel Programs

#### Question

Is the parallel efficiency of a parallel program independent of the number of processors  $\boldsymbol{p}$  used?

The question is answered by the concept of *parallel scalability*. Scientific computing and HPC distinguish two forms of scalability:

- **strong scalability** captures the dependence of the parallel runtime on the number of processors for a fixed total problem size.

- weak scalability captures the dependence of the parallel runtime on the number of processors for a fixed problem size per processor.

# CHAPTER 3

## Multicore and Multiprocessor Systems

| Contents |                                                            |          |

|----------|------------------------------------------------------------|----------|

| 3.1      | Symmetric Multiprocessing                                  | 3        |

| 3.2      | Memory Hierarchy                                           | 3        |

|          | 3.2.1 Basic Memory Layout                                  | 3        |

|          | 3.2.2 UMA                                                  | 3        |

|          | 3.2.3 NUMA                                                 | 3        |

|          | 3.2.4 ccNUMA                                               | 4        |

| 3.3      | Processes and Threads                                      | 4        |

|          | 3.3.1 Multiprocessing                                      | 4        |

|          | 3.3.2 Threading                                            | 5        |

|          | 3.3.3 Mapping of user level threads to kernel threads or   |          |

|          | processes                                                  | 5        |

|          | 3.3.4 Properties and Problems                              | <b>5</b> |

|          | 3.3.5 Protection of critical regions                       | 3        |

|          | 3.3.6 Dining Philosophers                                  | 9        |

| 3.4      | POSIX Threads                                              | )        |

|          | 3.4.1 Basics                                               | )        |

|          | 3.4.2 Creation of threads                                  | )        |

|          | 3.4.3 Exiting threads and waiting for their termination 31 | 1        |

| 3.5      | Pthread coordination mechanisms                            | 2        |

|          | 3.5.1 Mutex and condition variables                        | 2        |

|          | 3.5.2 Mutex variables 33                                   | )        |

3.5.6 A typical application example for semaphores . . . . 37

3.5.7 Coordination models for the cooperation of threads . 38

3.8.2

What OpenMP can do for us

43

3.8.3

What OpenMP is NOT for!

44

3.8.4

The Structure of the Standard

44

3.8.8 OpenMP runtime library functions . . . . . . . . . . . . 57

3.9.2 Basic idea of tree reduction . . . . . . . . . . . . . . . . . 59

3.9.3 Practical tree reduction on multiple cores . . . . . 60

3.10 Dense Linear Systems . . . . . . . . . . . . . . . . . 60

3.10.1 Repetition blocked algorithms . . . . . . . . . . . . . 60

3.10.2 Fork-Join parallel implementation for multicore ma-

3.10.3 DAG scheduling of block operations aiming at many-

3.11.1 The Conjugate Gradient (CG) Method (a prototype

3.11.7 Issues of Sparse Direct Solvers . . . . . . . . . . . . 69

3.11.8 A Task Pool Approach to Parallel Triangular Solves . 72

## 3.1 Symmetric Multiprocessing

**Definition 3.1** (Symmetric Multiprocessing (SMP)):

The situation where two or more identical processing elements access a shared periphery (i.e., memory, I/O,...) is called *symmetric multiprocessing* or simply (SMP).

The most common examples are

- Multiprocessor systems, where the processing elements are the single processors,

- Multicore CPUs, where the processing elements are given by the single cores

### 3.2 Memory Hierarchy

#### 3.2.1 Basic Memory Layout

#### 3.2.2 Uniform Memory Access (UMA)

UMA is a shared memory computer model, where

- · one physical memory resource,

- · is shared among all processing units,

- · all having uniform access to it.

Especially, that means that all memory locations can be requested by all processors at the same time scale, independent of which processor performs the request and which chip in the memory holds the location.

Local caches one the single processing units are allowed. That means classical multicore chips are an example of a UMA system.

#### 3.2.3 Non-Uniform Memory Access (NUMA)

Contrasting the UMA model in NUMA the system consists of

- · one logical shared memory unit,

- · gathered from two or more physical resources,

- each bound to (groups of) single processing units.

Due to the distributed nature of the memory, access times vary depending on whether the request goes to local or foreign memory.

Figure 3.1: AMDs Bulldozer layout is a NUMA example.

By The Portable Hardware Locality (hwloc) Project (Raysonho@Open Grid Scheduler / Grid Engine) [see web page for license], via Wikimedia Commons

Examples are current multiprocessor systems with multicore processors per socket and a separate portion of the memory controlled by each socket, or "cluster on a chip" design processors like AMDs bulldozer series.

#### 3.2.4 Cache Coherence

#### **Definition 3.2** (cache coherence):

The problem of keeping multiple copies of a single piece of data in the local caches of the different processors, that hold it, consistent is called *cache coherence* problem.

Cache coherence protocols:

- guarantee a consistent view of the main memory at any time.

- · Several protocols exist.

- Basic idea is to invalidate all other copies whenever one of them is updated.

#### 3.3 Processes and Threads

#### 3.3.1 Multiprocessing

#### **Definition 3.3** (Process):

A computer program in execution is called a process.

A process consists of:

- · the programs machine code,

- · the program data worked on,

- the current execution state, i.e., the context of the process, register and cache contents, . . .

Each process has a separate address space in the main memory.

Execution time slices are assigned to the active processes by the operating system's (OS's) scheduler. A switch of processes requires exchanging the process context, i.e., a short execution delay.

Multiple processes may be used for the parallel execution of compute tasks.

On Unix/Linux systems the fork () system call can be used to generate child processes. Each child process is generated as a copy of the calling parent process. It receives an exact copy of the address space of the parent and a new unique process ID (PID).

Communication between parent and child processes can be implemented via sockets or files, which usually leads to large overhead for data exchange.

#### 3.3.2 Threading

#### **Definition 3.4** (Thread):

In the thread model, a process may consist of several execution sub-entities, i.e control flows, progressing at the same time. These are usually called *threads*, or *lightweight processes*.

All threads of a process share the same address space. Thus communication and thread generation is simple and fast. There is no need to exchange data since everything is shared anyway.

Two types of implementations exist:

- · user level threads:

- administration and scheduling in user space,

- threading library maps the threads into the parent process,

- quick task switches avoiding the OS.

#### · kernel threads:

- administration and scheduling by OS kernel and scheduler,

- different threads of the same process may run on different processors

- blocking of single threads does not block the entire process,

- thread switches require OS context switches.

Here we concentrate on POSIX threads, or Pthreads. These are available on all major OSes. The actual implementations range from user space wrappers (pthreads-w32 mapping pthreads to windows threads) to lightweight process type implementations (e.g. Solaris 2).

#### 3.3.3 Mapping of user level threads to kernel threads or processes

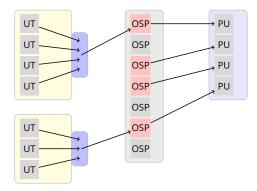

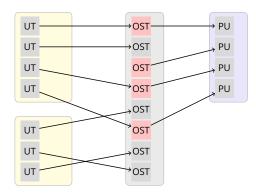

Figure 3.2: N:1 mapping for OS incapable of kernel threads

#### 3.3.4 Properties and Problems

#### Parallel versus concurrent execution

- 1. Often the two notions *parallel* and *concurrent* execution are used as synonyms of each other. In fact concurrent is more general.

- 2. The parallel execution of a set of tasks requires parallel hardware on which they can be executed simultaneously.

Figure 3.3: 1:1 mapping of user threads to kernel threads

- 3. The concurrent execution only requires a quasi parallel environment that allows all tasks to be in progress at the same time.

- 4. That means "parallel" execution defines a subset of "concurrent" execution.

#### Definition 3.5 (race condition):

When several threads/processes of a parallel program have read and write access to a common piece of data, access needs to be mutually exclusive. Failure to ensure this, leads to a race condition, where the final value depends on the sequence of uncontrollable/random events. Usually data corruption is then unavoidable.

### Example 3.6:

| Thread 1  | Thread 2  | value |

|-----------|-----------|-------|

|           |           | 0     |

| read      |           | 0     |

| increment |           | 0     |

| write     |           | 1     |

|           | read      | 1     |

|           | increment | 1     |

|           | write     | 2     |

| Thread 1  | Thread 2  | value |

|-----------|-----------|-------|

|           |           | 0     |

| read      |           | 0     |

|           | read      | 0     |

| increment |           | 0     |

| write     |           | 1     |

|           | increment | 1     |

|           | write     | 1     |

UT OST PU

UT OST PU

UT OST PU

UT OST PU

UT OST OST OST OST

Figure 3.4: N:M mapping of user threads to kernel threads with library thread scheduler

#### 3.3.5 Protection of critical regions

#### Definition 3.7 (semaphore):

A *semaphore* is a simple flag (binary semaphore) or a counter (counting semaphore) indicating the availability of shared resources in a critical region.

#### **Definition 3.8** (mutual exclusion variable (mutex)):

The mutual exclusion variable, or shortly mutex variable, implements a simple locking mechanism regarding the critical region. Each process/thread checks the lock upon entry to the region. If it is open the process/thread enters and locks it behind. Thus, all other processes/threads are prevented from entering and the process in the critical region has exclusive access to the shared data. When exiting the region the lock is opened.

Both the above definitions introduce the programming models. Actual implementations may be more or less complete. For example the pthreads-implementation lacks counting semaphores.

### Definition 3.9 (deadlock):

A *deadlock* describes the unfortunate situation, when semaphores, or mutexes have not, or have inappropriately been applied such that no pro-

cess/thread is able to enter the critical region anymore and the parallel program is unable to proceed.

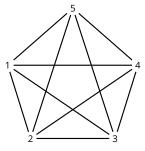

#### 3.3.6 Dining Philosophers

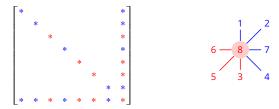

Figure 3.5: The dining philosophers problem

#### Example 3.10 (dining philosophers):

- · Each philosopher alternatingly eats or thinks,

- · to eat the left and right forks are both required,

- · every fork can only be used by one philosopher at a time,

- · forks must be put back after eating.

Image by Benjamin D. Esham / Wikimedia Commons [CC-BY-SA-3.0 (http://creativecommons.org/licenses/by-sa/3.0)]

#### simple solution attempt

- think until the left fork is available; when it is, pick it up;

- think until the right fork is available; when it is, pick it up;

- · when both forks are held, eat for a fixed amount of time;

- then, put the right fork down;

- · then, put the left fork down;

- · repeat from the beginning.

All philosophers decide to eat at the same time  $\Rightarrow$  deadlock.

More sophisticated solutions avoiding the deadlocks have been found since [4]. Three of them are also available on Wikipedia<sup>1</sup>.

#### 3.4 POSIX Threads

#### 3.4.1 Basics

Common to all the following commands:

Compiling and linking needs to be performed with -pthread (for GNU and Intel compilers).

The pthread functions and related data types are made available in a C program using:

```

#include <pthread.h>

```

#### 3.4.2 Creation of threads

- thread unique identifier to distinguish from other threads,

- attr attributes for determining thread properties. NULL means default properties,

- start\_routine pointer to the function to be started in the newly created thread.

- arg the argument of the above function.

Note that only a single argument can be passed to the threads start function.

The argument of the start function is a void pointer. We can thus define:

```

struct point3d{ double x,y,z; };

struct norm_args{

struct point3d *P;

double norm;

};

struct norm_args args;

```

and upon thread creation pass

```

err=pthread_create(tid, NULL, norm, (void *) &args);

```

to a start function

```

void *norm(void *arg) {

struct norm_args *args=(struct norm_args *) arg;

struct point3d *P;

P = args->P;

args->norm = P->x * P->x + P->y * P->y + P->z * P->z;

return NULL;

};

```

```

int main(int argc, char* argv[]) {

pthread_t tid1,tid2;

struct point3d point;

struct norm_args args;

args.P = &point;

point.x=10; point.y=10; point.z=0;

pthread_create(&tid1, NULL, norm, &args);

point.x=20; point.y=20; point.z=-50;

pthread_create(&tid2, NULL, norm, &args);

pthread_join(tid1, NULL);

pthread_join(tid2, NULL);

}

```

Depending on the execution of thread tid1 the argument point may get overwritten before it has been fetched, the analogue holds for the norm argument inside the function.

#### 3.4.3 Exiting threads and waiting for their termination

Pthreads can exit in different forms:

- · they return from their start function,

- they call pthread\_exit() to cleanly exit,

- they are aborted by a call to pthread\_cancel(),

- the process they are associated to is terminated by an exit () call.

```

int pthread_exit(void *retval);

```

retval return value of the exiting thread to the calling thread,

<sup>1</sup>http://en.wikipedia.org/wiki/Dining\_philosophers\_problem

- threads exit implicitly when their start function is exited,

- the return value may be evaluated from another thread of the same process via the pthread\_join() function,

- after the last thread in a process exits the process terminates calling exit ()

with a zero return value. Only then shared resources are released automatically.

```

int pthread_join(pthread_t thread, void **retval);

```

- · Waits for a thread to terminate and fetches its return value.

- thread the identifier of the thread to wait for,

- retval destination to copy the return value (if not NULL) to.

#### 3.5 Pthread coordination mechanisms

#### 3.5.1 Mutex and condition variables

The Pthread standard supports four types of synchronization and coordination facilities:

- 1. pthread\_join(); we have seen this function above

- 2. Mutex variable functions for handling mutexes as defined above

- 3. Condition variable functions treat a condition variable that can be used to indicate a certain event in which the threads are interested. Condition variables may be used to implement semaphore like structures and triggers for special more complex situation that require the threads to act in a certain way.

- 4. pthread\_once() can be used to make sure that certain initializations are performed by one and only one thread when called by multiple ones.

#### 3.5.2 Mutex variables

A mutex variable needs to be initialized before its first use. This can be done in two ways.

Dynamic initialization:

Static/Macro initialization:

```

pthread mutex t mutex = PTHREAD MUTEX INITIALIZER;

```

- mutex is the mutex variable to be initialized

- attr can be used to adapt the mutex properties, as for the pthreads NULL gives the default attributes,

- restrict<sup>2</sup> is a C99-standard keyword limiting the pointer aliasing features and guiding compilers and aiding in the caching optimization.

- initialization may fail if the system has insufficient memory (error code ENOMEM) or other resources (EAGAIN)

```

int pthread_mutex_lock(pthread_mutex_t *mutex);

```

- If mutex is unlocked the function returns with the mutex in locked state,

- If mutex is already locked the execution is blocked until the lock is released and it can proceed as above,

- Four types of mutexes are defined:

- PTHREAD MUTEX NORMAL

- PTHREAD\_MUTEX\_ERRORCHECK

- PTHREAD\_MUTEX\_RECURSIVE

- PTHREAD\_MUTEX\_DEFAULT

All of them show different behavior when locked mutexes should again be locked by the same thread or a thread tries to unlock a previously unlocked mutex and similar unintended situations. This, especially, regards error handling and deadlock detection.

#### int pthread\_mutex\_trylock(pthread\_mutex\_t \*mutex);

- The function is equivalent to pthread\_mutex\_lock(), except that it returns immediately in any case.

- Success or failure are determined from the return value.

- If the mutex type is PTHREAD\_MUTEX\_RECURSIVE the lock count is increased by one and the function returns success.

#### int pthread\_mutex\_unlock(pthread\_mutex\_t \*mutex);

- · the function releases the lock

- what exactly "release" means, depends on the properties of the mutex variable

<sup>&</sup>lt;sup>2</sup>For further information refer to the C99 standard [12] or the brief description at https://en.wikipedia.org/wiki/Restrict

- e.g., for type PTHREAD MUTEX RECURSIVE mutexes it means that the counter is decreased by one and they become available once it reaches zero

- if the mutex becomes available, i.e., unlocked by the function call and there are blocked threads waiting for it, the threading policy decides which thread acquires mutex next.

int pthread\_mutex\_destroy(pthread\_mutex\_t \*mutex);

- destroys the mutex referenced by mutex

- the destroyed mutex then becomes uninitialized

- pthread\_mutex\_init () can be used to initialize the same mutex variable again

- if mutex is locked or referenced, pthread\_mutex\_destroy() fails with error code EBUSY

#### 3.5.3 Avoiding mutex triggered deadlocks

**Example 3.11** (A deadlock situation when locking multiple mutexes): Problem:

- Consider two mutex variables ma and mb, as well as two threads T1 and T2.

- T1 locks ma first and then mb.

- T2 locks mb first and then ma.

- If T1 is interrupted by the scheduler after locking ma, but before locking mb and in the meantime T2 succeeds in locking it, then the classical deadlock occurs.

Locking hierarchy solution: The basic idea, here, is that all threads need to lock the critical mutexes in the same order. This can easily be guaranteed by hierarchically ordering the mutexes.

**Back off strategy solution:** When we want to keep the differing locking orders, we may use pthread\_mutex\_trylock() with a back off strategy.

- · Locking is tried in the desired order,

- when a trylock fails, the thread unlocks all previously locked mutexes (it backs off of the protected resources),

- after the back off it starts over from the first one.

#### 3.5.4 Condition variables

3.5. Pthread coordination mechanisms

Dynamic initialization:

```

int pthread_cond_init(pthread_cond_t *restrict cond,

const pthread_condattr_t *restrict

attr);

```

Static/Macro initialization:

```

pthread_cond_t cond = PTHREAD_COND_INITIALIZER;

```

- · cond the condition to be initialized

- attr can be used to adapt the condition properties, as for the pthreads NULL gives the default attributes,

- restrict: see pthread\_mutex\_init()

- · every condition variable is associated to a mutex.

```

int pthread_cond_destroy(pthread_cond_t *cond);

```

- · destroys the condition variable referenced by cond

- · the destroyed condition then becomes uninitialized

- pthread\_cond\_init() can reinitialize the same condition variable

- if cond is blocking threads when destroyed the standard does not specify the behavior of pthread\_cond\_destroy().

```

int pthread_cond_wait(pthread_cond_t *restrict cond,

pthread_mutex_t *restrict mutex);

```

- assumes that mutex was locked before by the calling thread,

- results in the thread getting blocked and at the same time (atomically) releasing mutex

- another thread may evaluate this to wake up the now blocked thread (see pthread\_cond\_signal())

- $\bullet$  upon waking up the thread automatically tries to gain access to  $\mathtt{mutex}$

- if it succeeds it should test the condition again to check whether another thread changed it in the meantime.

```

int pthread_cond_signal(pthread_cond_t *cond);

```

- if no thread is blocked on the condition variable cond there is no effect.

- · otherwise, one of the waiting threads is woken up and proceeds as described above.

```

int pthread_cond_broadcast(pthread_cond_t *cond);

```

- · wakes up all threads blocking on cond,

- · all of them try to acquire the associated mutex,

- · only one of them can succeed,

- · the others get blocked on the mutex now.

- equivalent to pthread\_cond\_wait() except that it only blocks for the period specified by abstime,

- if the thread did not get signaled or broadcast before abstime expires it returns with error code ETIMEDOUT.

#### 3.5.5 A counting semaphore for Pthreads

Semaphores are not available in the POSIX Threads standard.

However, they can be created using the existing mechanisms of mutexes and conditions.

A counting semaphore should be a data type that acts like a counter with non-negative values and for which two operations are defined:

- A signal operation increments the counter and wakes up a task blocked on the semaphore if one exists.

- 2. A wait operation simply decrements the counter if it is positive. If it was zero already the thread is blocking on the semaphore.

- · data structure for the semaphore:

```

typedef struct _sema_t{

int count;

pthread_mutex_t m;

pthread_cond_t c;

} sema_t;

```

the initialization

```

void InitSema(sema_t *ps) {

pthread_mutex_init(&ps->m, NULL);

pthread_cond_init(&ps->c, NULL);

}

```

· and the cleanup

```

void CleanupSema(void *arg) {

pthread_mutex_unlock((pthread_mutex_t *) arg);

}

```

```

void ReleaseSema (sema_t *ps) { // signal operation

pthread_mutex_lock(&ps->m) ;

pthread_cleanup_push(CleanupSema, &ps->m);

{

ps->count++;

pthread_cond_signal(&ps->c) ;

}

pthread_cleanup_pop ( 1 ) ;

}

void AcquireSema (sema_t *ps) { // wait operation

pthread_mutex_lock(&ps->mutex);

pthread_cleanup_push(CleanupSema, &ps->m);

{

while(ps->count==0)

pthread_cond_wait(&ps->c, &ps->m) ;

ps->count--;

}

pthread_cleanup_pop(1);

}

```

#### 3.5.6 A typical application example for semaphores

**Example 3.12** (Producer/Consumer queue buffer protection): Basic setup:

- A buffer of fixed size n is shared by

- a producer thread generating entries and storing them in the buffer if it is not full,

- a consumer thread removing entries from the same buffer for further processing unless it is empty.

For the realization of the protected access two semaphores are required:

- 1. Number of entries occupied (initialized by 0),

- 2. Number of free entries (initialized by n).

The Mechanism works for an arbitrary number of producers and consumers.

#### 3.5.7 Coordination models for the cooperation of threads

- 1. Master/Slave model:

- · A master thread is controlling the execution of the program,

- the slave threads are executing the work.

- 2. Client/Server model:

- · Client threads produce requests,

- · Server threads execute the corresponding work.

- 3. Pipeline model:

- Every thread (except for the first and last in line) produces output that serves as input for another thread,

- after a startup phase (filling the pipeline) the parallel execution is achieved.

- 4. Worker model:

- · equally privileged workers organize their workload,

- an important variant is the task pool treated as detailed example next.

#### 3.6 Task Pools

#### 3.6.1 Basic idea of the task pool

#### Idea:

Creation of a parallel threaded program that can dynamically schedule tasks on the available processors. This enables us to work on highly irregular problems like adaptive or hierarchical algorithms, as well as unbalanced problems like the sparse matrix vector product with strongly varying numbers of elements per row, much more efficiently.

#### Key ingredients in the approach are:

- · usage of a fixed number of threads

- · organization of the pending tasks in a task pool,

- threads fetch the tasks from the pool and execute them leading to a dynamic assignment of the work load.

#### Main advantages

- automatic dynamic load balancing among the threads

- comparably small overhead for the administration of threads

#### 3.6.2 Implementation of a basic task pool

#### **Data structures**

· data strucutre for one task:

```

typedef struct _work_t{

void (*routine) (void*); //worker function to call

void* arg;

struct _work_t *next;

} work_t;

```

• data structure for the task pool:

```

typedef struct _tpool_t{

int num_threads ; // number of threads

int max_size, curr_size; // max./cur. number of

tasks in pool

pthread_t *threads; //array of threads

work_t *head , *tail; // start/end of the task

queue

pthread_mutex_t lock; //access control for the task

pool

pthread_cond_t not_empty ; // tasks are available

pthread_cond_t not_full ; // tasks may be added

} tpool_t ;

```

#### Initialization

```

tpool_t *tpool_init(int num_threads , int max_size) {

int i;

tpool_t *tpl;

tpl=(tpool_t *) malloc (sizeof(tpool_t));

tpl->num_threads=num_threads ;

tpl->max_size=max_size ;

tpl->cur_size=0;

```

#### **Worker Threads**

```

void *tpool thread(void *vtpl) {

tpool_t *tpl=(tpool_t *) vtpl;

work t *wl;

for (;;) {

pthread_mutex_lock(&tpl->lock);

while(tpl->cur size==0)

pthread_cond_wait(&tpl->not_empty , &tpl->lock);

wl=tpl->head; tpl->cur_size--;

if(tpl->cur_size==0)

tpl->head=tpl->tail=NULL;

else tpl->head = wl->next;

if (tpl->cur_size==tpl->max_size-1) // pool full

pthread_cond_signal(&tpl->not_full);

pthread_mutex_unlock(&tpl->lock);

(*(wl->routine)) (wl->arg);

free(wl);

```

#### **Task insertion**

```

void tpool_insert(tpool_t *tpl, void(*f) (void*), void *arg

) {

work_t *wl ;

pthread_mutex_lock(&tpl->lock);

while(tpl->cur_size==tpl->max_size)

pthread_cond_wait(&tpl->not_full, &tpl->lock);

wl=(work_t *) malloc(sizeof(work_t));

wl->routine=f; wl->arg=arg; wl->next=NULL;

if( tpl->cur_size==0) {

tpl->head=tpl->tail=wl;

pthread_cond_signal(&tpl->not_empty);

}

}

```

```

}

else{

tpl->tail->next=wl; tpl->tail=wl;

}

tpl->cur_size++;

pthread_mutex_unlock(&tpl->lock);

}

```

### 3.7 Shared Memory Blocks

#### 3.7.1 General shared memory blocks

In contrast to Threads, different processes do not share their address space. Therefore, different ways to communicate in multiprocessing applications are necessary.

One possible way are shared memory objects. Unix-like operating systems provide at least one of:

- old: System V Release 4 (SVR4) Shared Memory<sup>3</sup>

- **new:** POSIX Shared Memory<sup>4</sup>.

Both techniques implement shared memory objects, like common memory, semaphores and message queues, which are accessible from different applications with different address spaces.

#### 3.7.2 POSIX Shared Memory

#### **Common Memory Locations**

- They are used to share data between applications.

- They are managed by the kernel and not by the application.

- Each location is represented as a file in /dev/shm/.

- · They are handled like normal files.

- They are created using shm\_open and mapped to the memory using mmap.

- Exist as long as no application deletes them.

- · Even when the creating program exits they stay available,

<sup>&</sup>lt;sup>3</sup>System V Interface Definition, AT&T Unix System Laboratories, 1991

<sup>&</sup>lt;sup>4</sup>IEEE Std 1003.1-2001Portable Operating System Interface System Interfaces

• See manpage: man 7 shm\_overview.

#### **POSIX Semaphores**

- Counting semaphores are available form different address spaces.

- They correspond to pthread\_mutex\_\* in threaded applications.

- They are represented as a file in /dev/shm/sem.\*.

- See manpage: man 7 sem\_overview.

#### **Message Queues**

- They represent a generalized Signal concept which can transfer a small payload (2 to 4 KiB).

- They correspond to pthread\_cond\_\* in threaded applications.

- They can be represented as file in /dev/mqueue.

- See manpage: man 7 mq\_overview.

### 3.8 Open Multi-Processing (OpenMP)

#### 3.8.1 This is OpenMP

#### Mission

"The OpenMP Application Program Interface (API) supports multi-platform shared-memory parallel programming in C/C++ and Fortran on all architectures, including Unix platforms and Windows NT platforms. Jointly defined by a group of major computer hardware and software vendors, OpenMP is a portable, scalable model that gives shared-memory parallel programmers a simple and flexible interface for developing parallel applications for platforms ranging from the desktop to the supercomputer." a

#### The OpenMP Architecture Review Board (ARB)

The ARB is a non-profit enterprise owning the OpenMP brand and responsible for overseeing, producing and approving the OpenMP standards.

#### Members of the ARB include:

(status: April 22, 2021)

- · Hardware manufacturers: e.g. AMD, NVidia, IBM, NEC, HP

- Software companies: e.g. Oracle, SuSe

- Compute centers: e.g. Sandia NL, Lawrence Livermore NL, CSC, Leibniz Supercomputing Center, Barcelona Supercomuting Center

- Universities: e.g. University of Tennessee, RWTH Aachen, Uni Basel, Uni Bristol

Complete list available at: http://www.openmp.org/about/members/

#### History

```

Oct. 1997 OpenMP 1.0 for Fortran,

```

Oct. 1998 OpenMP 1.0 for C/C++,

Nov. 2000 OpenMP 2.0 for Fortran,

March 2002 OpenMP 2.0 for C/C++,

May 2005 OpenMP 2.5 (first joint Fortran/C/C++ version),

May 2008 OpenMP 3.0,

Sept. 2011 OpenMP 3.1,

July 2013 OpenMP 4.0,

Nov. 2015 OpenMP 4.5,

Nov. 2018 OpenMP 5.0,

Nov. 2020 OpenMP 5.1 (current standard)

#### 3.8.2 What OpenMP can do for us

- Easy shared memory parallel adaption of existing sequential codes

- Easy preservation of sequential implementations

- Easy porting to different platforms and compilers

- · Parallel implementation of only fragments

- · No extra runtime environment

- · Easy to learn and apply

<sup>&</sup>lt;sup>a</sup>The Mission statement from http://www.openmp.org/about/about-us/

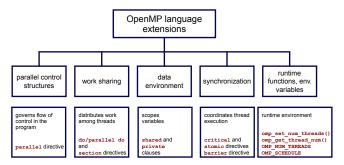

Figure 3.6: Classification of the OpenMP extensions by tasks of the elements (Image Source: https://commons.wikimedia.org/wiki/File:OpenMP\_language\_extensions.svg).

#### 3.8.3 What OpenMP is NOT for!

- · Distributed memory parallel systems (by itself)

- · Most efficient use of shared memory systems

- Automatic checking for (data dependencies,) data conflicts, race conditions, or deadlocks

- Automatic synchronization of input and output

#### 3.8.4 The Structure of the Standard

The standard divides the extensions into four classes:

- Directives: Basic control structures that initialize/end the parallel environments

- 2. Clauses: Fine tuning parameters added to the directives.

- 3. **Environment Variables:** Variables in the calling shell used to control the parallel environment without recompilation.

- 4. **Runtime Library Routines:** Runtime usable functions for the determination and modification of parameters of the parallel environment.

#### 3.8.5 OpenMP directives

The #pragma directive was introduced in C89 as the universal method for extending the space of directives. It was further standardized in C99, where especially the token STDC was reserved for standard C extensions.

In part 1 of the Scientific Computing lecture we have seen the floating point environment for, e.g., checking the exception flags in IEEE arithmetic:

```

#include <fenv.h>

#pragma STDC FENV_ACCESS ON

/* starting here the compiler needs to assume we are

accessing the

floating point status and mode registers*/

```

OpenMP is an extension in the sense of C89 and enabled by the

```

#pragma omp

```

preprocessor directive. It applies to the succeeding structural code block. That means, it applies to the next single line of code, a block encapsulated by a C control structure (e.g. a for-loop), or a portion of code enclosed by { }.

Compilers that do not know the omp pragma simply ignore it. The following switches enable OpenMP support for your code compilation:

| GNU GCC    | -fopenmp |

|------------|----------|

| Intel ICC  | -qopenmp |

| LLVM CLANG | -fopenmp |

| IBM XLC    | -qsmp    |

| PGI        | -mp      |

Otherwise the  ${\tt omp}$  pragmas are ignored and the sequential code version is compiled.

A list of compilers supporting OpenMP can be found at https://www.openmp.org/resources/openmp-compilers-tools/

The following versions of the OpenMP standard are currently supported by the GCC compiler (April 2017):

OpenMP 2.5 starting from GCC 4.2.0,

**OpenMP 3.0** starting from GCC 4.4.0,

OpenMP 3.1 starting from GCC 4.7.0,

OpenMP 4.0 starting from GCC 4.9.1,

**OpenMP 4.5** starting from GCC 6.1.0 (except of gfortran (planned for GCC 11)).

In the following we give a brief list of the most classic directives with their most basic clauses. The recent standards extend, both, the list of directives and the

**omp parallel directive.** The *parallel* construct initializes a group of threads and starts parallel execution:

```

#pragma omp parallel [clause[[,]clause]...]

```

The clauses can be used to influence the behavior of the parallel execution. They will be explained in Section 3.8.6.

Available clauses for parallel:

- if(scalar expression)

- num\_threads(integer expression)

- default(shared| none)

- private(list)

- firstprivate(list)

- shared(list)

- copyin(list)

- reduction(operation:list)

#### **Example 3.14** (A minimal OpenMP parallel "hello world" program):

```

#include <stdio.h>

int main(void)

{

#pragma omp parallel

printf("Hello,_world.\n");

return 0;

}

```

Example 3.14 automatically lets OpenMP tune the number of threads used to the number of available processors. Afterward the parallel execution environment is started and all threads execute the printf statement.

**omp loop directive.** The loop construct specifies that the iterations of the loop should be distributed among the active threads.

```

#pragma omp for [clause[[,]clause]...]

for loops

```

The for-loop construct needs to be used inside a structured code block of a parallel construct.

47

Available clauses for for:

```

private(list)

```

- firstprivate(list)

- lastprivate(list)

- reduction(operator:list)

- schedule(kind[,chunk\_size])

- · collapse(n)

- · ordered

- nowait

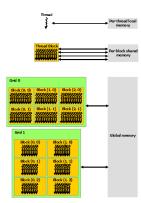

omp parallel loop directive. Since often the parallel environment

is used to introduce a for-loop construction only, a shortcut parallel for

exists for this special task

```

#pragma omp parallel for [clause[[,] clause]...]

```